RISC-V

RISC-V (pronounced “risk-five”) is an open standard instruction set architecture (ISA) based on established reduced instruction set computing (RISC) principles. Unlike proprietary ISAs, the RISC-V ISA is provided under open source licenses that do not require fees to use. This openness allows any organization or individual to design, manufacture, and sell RISC-V chips and software without paying royalties.

Research

Our research implies RISC-V on multi-core interconnection, processor soft error resilience strategy, and network packet processor architecture.

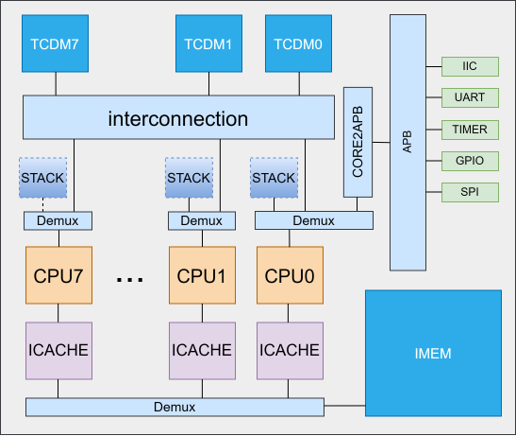

We designed the interconnection structure and programming framework for multi-core RISC-V architecture in edge computing scenarios, and implemented a complete runnable prototype of a multi-core processor. This architecture is named PULP-Lite. This project was sponsored by Nanjing Qinheng Microelectronics.

We explored processor soft error resilience strategy, and proposed a set of soft error detection and recovery mechanisms in a RISC-V in-order single-core processor.This innovation significantly improved the soft error reslience with reasonable performance and resource overhead. This work has resulted in a patent, and we plan to publish a paper. We continued our collaboration with Qinheng in this project.

Currently, we are collaborating with Sanechips to create a network packet processing scheme and specialized extended instructions based on RISC-V. Then we try to design a general network packet processor based on this architecture.

Collaborating Companies

Last edited in 2024.4